1/6.5 英寸 120 万像素 720P CMOS 图像传感器 SP1628

硬件设计指导手册

Version 1.3 2013.04.03

北京思比科微电子技术股份有限公司

SP1628 是 SuperPix 最新研发推出的 120 万像素 CMOS 图像传感器芯片,仅有 1/6.5 英寸大小的 SP1628 可提供 XVGA、720P 以及 VGA 多种格式图像,广泛适用于平板电脑、可拍照手机、整合式笔记本电脑摄像头等设备,为这类产品提供具有成本效益的解决方案。SP1628 基于 SuperPix 具有自主知识产权的第 2 代图像传感器技术和最新的 1.75 um 像素架构进行研发,该设计已经应用于多款系列产品,市场反映良好。SP1628 具有高感光度和低功耗的特性,其新增的 MIPI 接口功能,使 SP1628 能够实现更简洁和低功耗的数据传输方式,而改进的 50Hz/60Hz 抖动检测功能则能为用户提供更加清晰锐利的图像。

### 主要功能

- CMOS 图像传感器

- 图像处理

### 典型应用

- 移动电话

- 平板电脑

- PC 摄像头

- 网络摄像头

#### www.SuperPix.com.cn

北京市上地五街 7号吴海大厦 201

电话 86-10-82784282

传真 86-10-82784851

2013 北京思比科微电子技术股份有限公司

# 目录

| 第1章   | 参考设计   | 4  |

|-------|--------|----|

|       | MIPI模式 |    |

| 1.2   | 并口模式   | 6  |

| 第2章   | 封装信息   | 8  |

| 第3章   | 成像方向   | 12 |

| 第 4 章 | 版本历史   | 13 |

|       |        |    |

## 第1章 参考设计

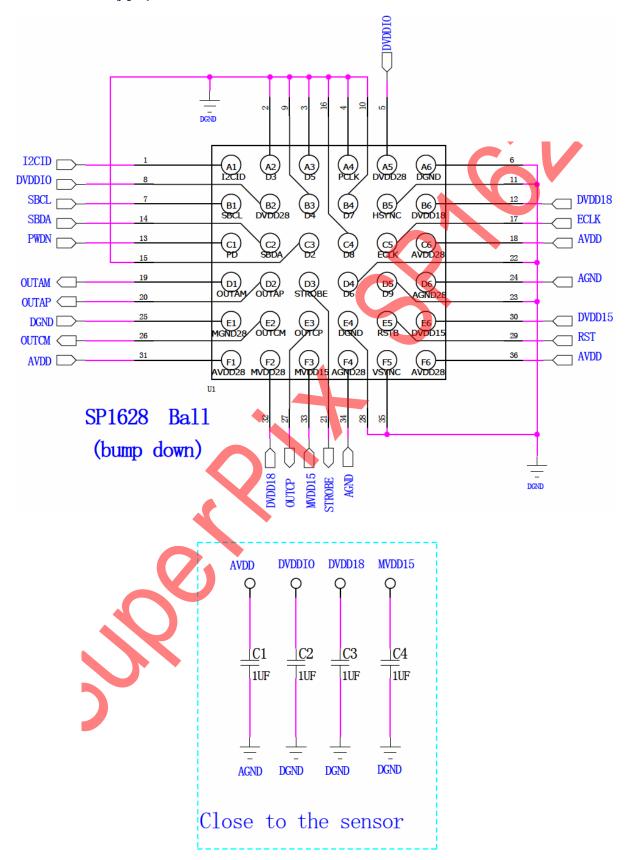

## 1.1 MIPI模式

Connector

图表 1 MIPI 模式参考设计

#### 注:

- 1. 此设计是 MIPI 模式, 并口管脚 D2-D9/HSYNC/VSYNC/PCLK 直接接地。若系统接口有 STROBE,则芯片的 STROBE 管脚引出,若没有,则芯片的 STROBE 管脚接地; I2CID 是 I2C 地址可控管脚,一般可直接接地。2. 电源 DVDDIO 可兼容 1. 8V/2. 8V,根据系统接口电气特性由系统设定; AVDD 必须为 2. 8V,若系统 DVDDIO 高于 2. 8V 时,那么 DVDDIO 和 AVDD 短接采用同一路电压输入; DVDD18 接 1. 8V; MVDD28 与 DVDD18 短接; MVDD15 接外部电容,不用引到 Connector 处; DVDD15 属于内部电源,悬空即可(不能拉低),不用引到 Connector 处;

- 3. PCB 设计时, 芯片必须得转 180° 放置,请参考芯片在模组中的摆放示意图(成像方向部分)。芯片电源滤波电容(最小一定要贴 0402 封装 1uf),请靠近电源管脚放置,电源应尽可能不细于 0. 2mm 设计, 地线拉网铺地;

- 4. OUTAP/OUTAM 和 OUTCP/OUTCM 是两对差分线,走线要尽可能等长等间距被地包着走,差分线底层(或 TOP 层)要有完整参考地,PCB 打样时要告诉PCB厂家哪些是差分线,要求厂家在制作时也要进行阻抗控制,阻抗标准100ohm,误差不能超过+-10%;

- 5. 模组生产时, FPC 采用抗干扰设计。

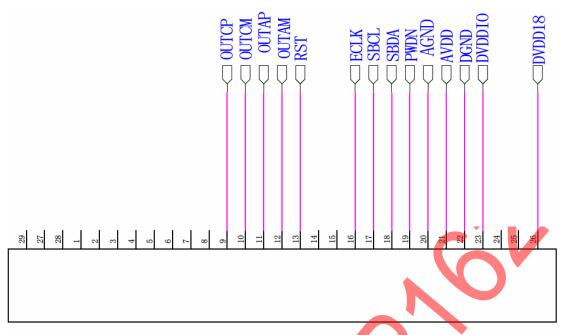

### 1.2 并口模式

Connector

#### 注:

- 1. 此设计是并口模式, OUTCM/OUTCP, OUTAM/OUTAP 悬空(不能拉低), STROBE 根据客户需要灵活添加到接口处; I2CID是 I2C地址可控管脚, 一般可直接接地。

- 2. 电源 DVDDIO 可兼容 1. 8V/2. 8V,根据系统接口电气特性由系统设定; AVDD 必须为 2. 8V; 若系统 DVDDIO 高于 2. 8V 时,那么 DVDDIO 和 AVDD 短接采用同一路电压输入; DVDD18 接 1. 8V; MVDD28 与 DVDD18 短接; MVDD15 接外部电容,不用引到 Connector 处; DVDD15 属于内部电源,悬空即可(不能拉低),不用引到 Connector 处;

- 3. PCB 设计时, 芯片必须得转 180° 放置, 请参考芯片在模组中的摆放示意图(成像方向部分)。芯片电源滤波电容(最小一定要贴 0402 封装 1uf), 请靠近电源管脚放置, 电源应尽可能不细于 0. 2mm 设计, 地线拉网铺地;

- 4. PCLK/HSYNC/VSYNC/D2-D9/I2C 走线尽可能平行等长设计,时钟走线尽可能短粗被地包着走;

- 5. 模组生产时, FPC 采用抗干扰设计。

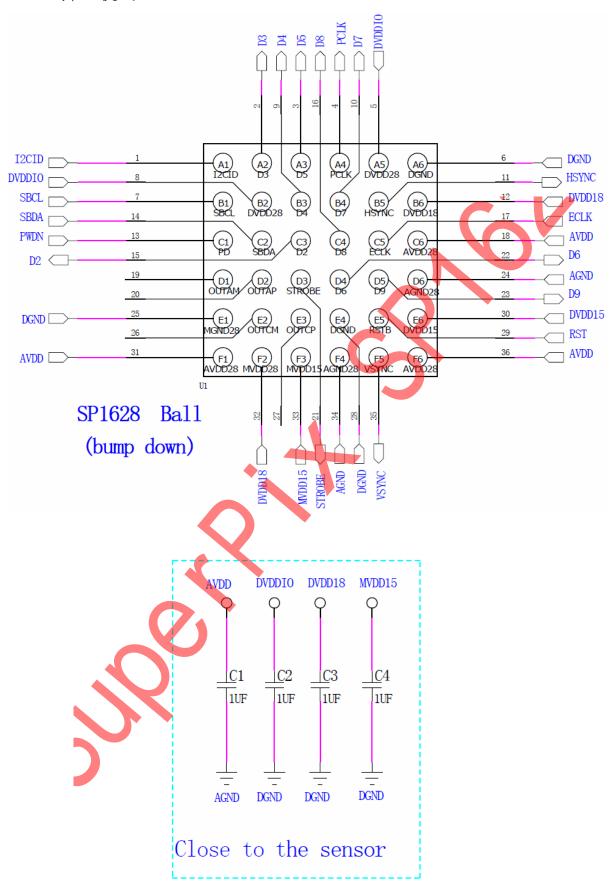

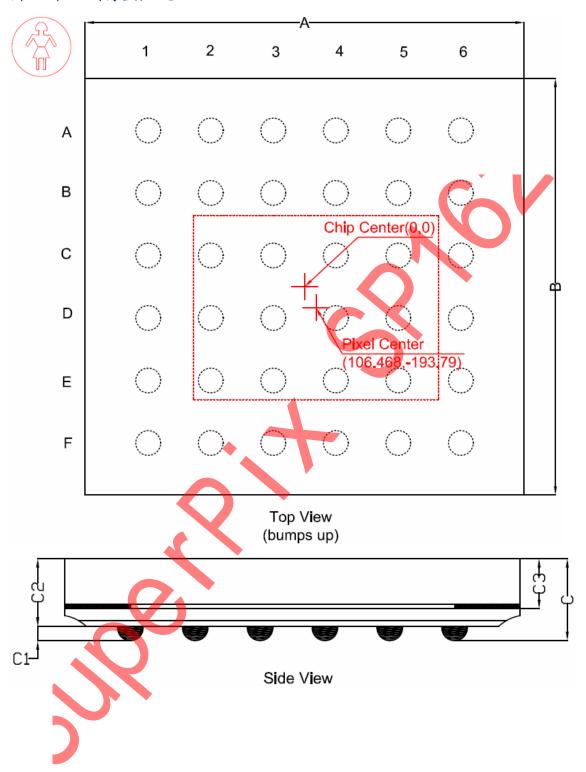

## 第2章 封装信息

图表 2 封装规格

Parameter Symbol Nominal Min. Max. Package Body Dimension X 4070 4045 4095 Α Package Body Dimension Y 3866 3841 3891 В Package He**i**ght 790 С 730 670 Ball Height 130 100 160 C1 Package Body Thickness C2 600 565 635 Thickness of glass surface to wafer 445 425 465 C3 Ball Diameter 230 200 260 D Total Ball count 36 Ν Pin pitch1 X axis J1 580 Pin pitch Y axls J2 580 Edge to Pin Center Distance along X S1 585 555 615 Edge to Pin Center Distance along Y S2 483 453 513

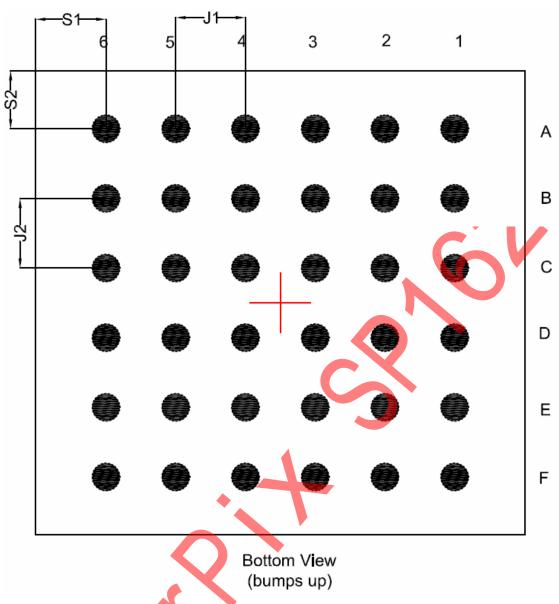

图表 3 封装尺寸

|   | 1      | 2      | 3      | 4      | 5      | 6      |

|---|--------|--------|--------|--------|--------|--------|

| Α | I2CID  | D3     | D5     | PCLK   | DVDD28 | DGND   |

| В | SBCL   | DVDD28 | D4     | D7     | HSYNC  | DVDD18 |

| С | PD     | SBDA   | D2     | D8     | ECLK   | AVDD28 |

| D | OUTAM  | OUTAP  | STROBE | D6     | D9     | AGND28 |

| Ē | MGND28 | OUTCM  | OUTCP  | DGND   | RSTB   | DVDD15 |

| F | AVDD28 | MVDD28 | MVDD15 | AGND28 | VSYNC  | AVDD28 |

图表 4 锡球阵列信息

| NO. | Pad Name | I/O    | Description                                                    |  |

|-----|----------|--------|----------------------------------------------------------------|--|

| A1  | I2CID    | _      | I2C Slave address select                                       |  |

| A2  | D3       | 0      | Pixel Array Output bit 3                                       |  |

| A3  | D5       | 0      | Pixel Array Output bit 5                                       |  |

| A4  | PCLK     | 0      | Pixel Output Clock                                             |  |

| A5  | DVDD28   | DP     | Digital Power 2.8V                                             |  |

| A6  | DGND     | DG     | Digital Ground                                                 |  |

| B1  | SBCL     | _      | Slave I2C clock bus                                            |  |

| B2  | DVDD28   | DP     | Digital Power 2.8V                                             |  |

| В3  | D4       | 0      | Pixel Array Output bit 4                                       |  |

| B4  | D7       | 0      | Pixel Array Output bit 7                                       |  |

| B5  | HSYNC    | 0      | Horizontal Sync Signal                                         |  |

| B6  | DVDD18   | DP     | Digital Power 1.8V                                             |  |

| C1  | PD       | _      | Power down,"0" normal                                          |  |

| C2  | SBDA     | 9      | Slave Tri-state,I2C data bus                                   |  |

| C3  | D2       | 0      | Pixel Array Output bit 2                                       |  |

| C4  | D8       | 0      | Pixel Array Output bit 8                                       |  |

| C5  | ECLK     | _      | Input system clock                                             |  |

| C6  | AVDD28   | AP     | Analog Power 2.8V                                              |  |

| D1  | OUTAM    | 0      | MIPI data output -                                             |  |

| D2  | OUTAP    | 0      | MIPI data output +                                             |  |

| D3  | STROBE   | 0      | Strobe Signal                                                  |  |

| D4  | D6       | 0      | Pixel Array Output bit 6                                       |  |

| D5  | D9       | 0      | Pixel Array Output bit 9                                       |  |

| D6  | AGND28   | AG     | Analog Ground                                                  |  |

| E1  | MGND28   | MG     | MIPI Ground                                                    |  |

| E2  | OUTCM    | 0      | MIPI clock output -                                            |  |

| E3  | OUTCP    | 0      | MIPI clock output +                                            |  |

| E4  | DGND     | DG     | Digital Ground                                                 |  |

| E5  | RSTB     | _(     | Reset Signal,Low level reset                                   |  |

| E6  | DVDD15   | DP     | While "BYPASS" Pin connect to "0", internal power supply 1.5V. |  |

| =0  | 540013   | DVDD13 | While "BYPASS" Pin connect to "1", external power supply 1.5V. |  |

| F1  | AVDD28   | AP     | Analog Power 2.8V                                              |  |

| F2  | MVDD28   | MP     | MIPI Power 1.8V                                                |  |

| F3  | MVDD15   | MP     | External Connect capacitance(1uF)                              |  |

| F4  | AGND28   | AG     | Analog Ground                                                  |  |

| F5  | VSYNC    | 0      | Vertical Sync Signal                                           |  |

| F6  | AVDD28   | AP     | Analog Power 2.8V                                              |  |

图表 5 Pin 定义

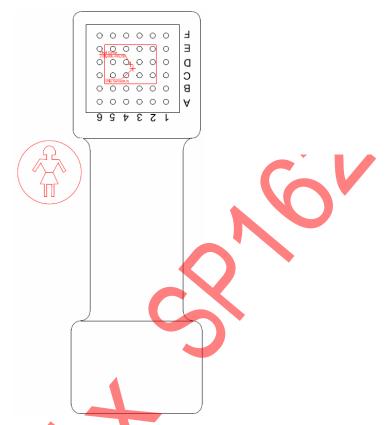

# 第3章 成像方向

图表 6 模组在芯片中的摆放示意图

图表 7 模组在电脑中的显示示意图

# 第4章 版本历史

| 版本                  | 日期           | 描述                                                            |

|---------------------|--------------|---------------------------------------------------------------|

| SP1628 硬件设计指导手册 1.0 | 2012. 12. 19 | 1. 第一版 for TSV , 参考设计 ref2012.12.19 V1.0, 封装 ref12/17-12 v1.0 |

| SP1628 硬件设计指导手册 1.1 | 2013.01.31   | 1. 修改参考设计注释                                                   |

| SP1628 硬件设计指导手册 1.2 | 2013.02.01   | 1. 修改参考设计, ref2013.1.31v2.0                                   |

| SP1628 硬件设计指导手册 1.3 | 2013. 04. 03 | 1. 修改参考设计注释, ref2013.4.3v3.0<br>2. 修改成像方向, 模组在芯片中的摆放示意图       |